苹果与台积电的合作推动了两家公司的成功。得益于与台积电的密切关系,Apple 推出了 A12X 处理器,这反过来推动了 2018 款 iPad Pro 与低功耗笔记本电脑并驾齐驱(并领先于)。没有其他科技公司的产品具有类似的性能范围和形式。现在,台积电着眼于未来,据报道该公司将于2021年开始量产3D芯片封装。台积电的WoW(Wafer-on-Wafer)封装源于该公司的InFO和CoWoS技术。看看下面的更多细节。

摩尔定律的放缓和先进制造工艺的复杂性,再加上当今日益增长的计算需求,让科技公司陷入了一个难题。我们看到诸如用于蚀刻的 EUV和用于多栅器件的GAAFET(全栅)等新技术为行业问题提供了创新的解决方案。

台积电(纽约证券交易所代码:TSM)故乡新竹在 6 月 1 日面临可能的水资源配给,因为的资源紧缩情况恶化

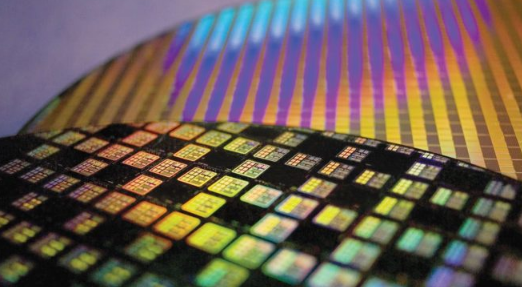

现在,随着它准备使用其7FF+ 工艺设计生产处理器,晶圆厂台积电已确认该公司将在 2021 年跳转到 3D 封装芯片。这一转变将允许其客户在内部“堆叠”多个 CPU 或 GPU单个封装 - 有效地将晶体管数量增加了一倍。为实现这一目标,台积电将使用 TSV(硅通孔)连接两个不同的芯片晶圆。

Stacked die 在存储领域很常见,台积电的 WoW 将把这个概念应用到计算芯片上。台积电与总部位于加利福尼亚的 Cadence Design Systems 合作开发了该技术,该技术是该公司InFO(集成扇出)和 CoWoS(基板上芯片)3D 芯片生产技术的延伸。该晶圆厂去年宣布了 WoW,现在,它将在 2021 年开始使用新技术进行制造。

从时间范围来看,WoW 很可能会与 5nm 一起使用。在 17nm 之后,5nm 将允许苹果等公司在其 SoC 上塞入多达 100 亿个晶体管,其表面积与当前的 A12 相似。台积电将通过将 3D 平面上的单独晶圆与 TSV(硅通孔)连接来实现堆叠。TSV 本质上是 10 微米的孔,可促进两个堆叠芯片之间的转移。如果我们真的看到了 5nm 的 WoW,那么开发人员可用于桌面和移动应用程序的计算能力将是 巨大的,喜欢 2018 年的 iPad?您将亲眼目睹平板电脑的计算能力翻了一番,但 5 纳米的足迹更小。我们还能奢望什么?