根据DigiTimes的最新报告,英伟达将成为今年将利用台积电CoWoS封装的三个主要客户之一,另外两个是Xilinx和HiSilicon。

CoWoS(基板上的晶片上芯片)是一种2.5D封装技术,可将多个小芯片集成到单个中介层上。主要的好处包括更小的占地面积,增加带宽和降低功耗。

谈到CoWoS,台积电(TSMC)与Broadcom(博通)最近合作开发了一种面积达1,700mm²的庞大内插器。总而言之,该概念包括将多个互连的中介层绑定在一个单独的晶圆上。这项新设计将在即将面世的Broadcom HPC(高性能计算)处理器中得到体现,该处理器基于TSMC的EUV 5nm(N5)节点。改进后的CoWoS平台可以容纳多个片上系统(SoC)芯片和多达6个HBM高带宽内存堆栈,总共可容纳多达96GB的内存。台积电宣称其高达2.7 TBps的内存带宽,比该公司于2016年推出的先前CoWoS平台快2.7倍。

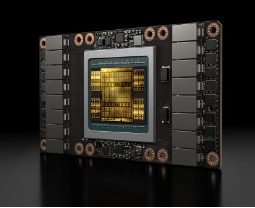

回到Nvidia,这家芯片制造商对CoWoS封装并不陌生。这项技术可追溯到Pascal时代,并出现在许多高端的Titan,Quadro和Tesla显卡上。GP100(Pascal)和GV100(Volta)硅粉是从台积电的熔炉中出来的,并使用CoWoS封装。第一种基于晶圆代工厂的16nm FinFET制造工艺,而后者则从12nm节点获利。

AMD的Vega 20 7nm芯片也与CoWoS封装在一起。DigiTimes并未将AMD列入前三名,这意味着Nvidia,Xilinx和HiSilicon最终将吞噬台积电的CoWoS生产能力。据报道,该铸造厂每月将抽出6,000至8,000个晶圆,因此应该有足够的产品可以运送。

无论如何,我们都不希望Nvidia的消费者图形卡采用CoWoS技术,因为它会给消费者带来高昂的成本。像过去一样,这家芯片制造商可能会向CoWoS寻求Quadro和Tesla的产品。安培(Ampere)是Nvidia下一代GPU架构的代号,但是没有迹象表明它将采用MCM(多芯片模块)设计。另一方面,料斗可能依赖MCM。

我们已经看到了三张神秘的Nvidia图形卡,其中包含大量的CUDA内核和内存。尽管我们不确定它们的性质,但未识别的图形卡应使用Nvidia即将推出的GPU架构之一。