在AMD第二代EPYC罗马处理器在八月推出和自那时以来,我们一直在获取有关芯片本身更多的细节与特点一起。Hardwareluxx透露了有关I / O芯片的最新细节,包括特写的芯片照片,使我们可以更好地了解AMD迄今为止最具创新性的服务器芯片。

AMD第二代EPYC Rome处理器IOD详细介绍-单芯片上的晶体管数量为83.4亿,整个芯片上的晶体管数量为395.4亿

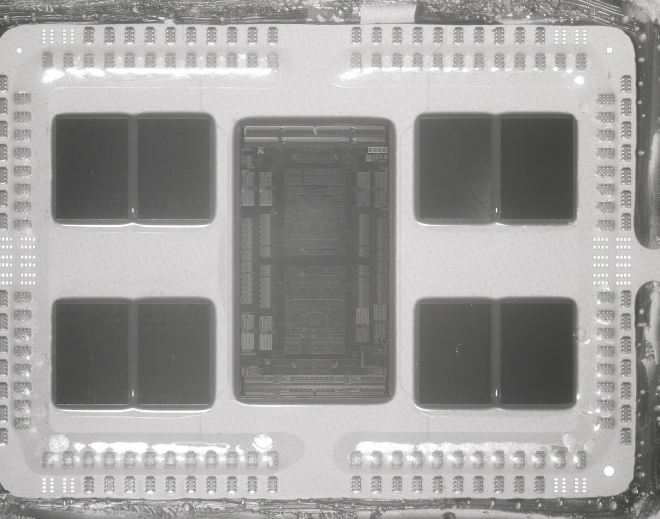

AMD最近刚刚开始透露其第二代EPYC Rome处理器的许多细节。AMD EPYC Rome处理器由9芯片设计组成,也称为MCM(多芯片模块)。9个芯片包括8个CCD(计算核心芯片)和一个IOD(输入/输出芯片)。每个CCD由两个CCX(计算核心复合体)组成,这些CCX具有四个Zen 2核心,分别具有各自的L2缓存和共享的L3缓存。所有八个CCD都使用无穷大结构连接到I / O裸片。

每个CCD的面积为74mm2,由39亿个晶体管组成。Ryzen上的IOD芯片尺寸为125mm2,由20.9亿个晶体管组成。EPYC上的IOD由83.4亿个晶体管组成,尺寸为416mm2。它是第二代EPYC芯片上最大的芯片。IOD结合了8 Zen 2 CCD的1008mm2尺寸,同时由395.4亿个晶体管组成。

现在,其中一个的IOD比Ryzen处理器的IOD大得多。这是由于服务器平台的功能要求更高。通过使用透射照明进行曝光时,IO裸片将清晰地暴露,并且内部块可以清晰地暴露出来。

据说,IOD的大部分中央空间专用于SRAM和纵横开关,而PCIe Gen 4接口位于IOD的侧面。芯片的上部和下部具有四个72位DDR4存储器通道。现在,这是有趣的部分,EPYC 2nd Gen能够通过PCIe Gen 4提供两倍的带宽,并减少Infinity Fabric对总线的依赖,从而在计划于以后推出的定制处理器上暴露更多的通道,从而能够扩展至162个PCIe通道。 。额外的PCIe通道已经存在,但已被互连使用。

除了IOD,Zen 2 CCD或Compute Core Die还从Flickr的OC_Burner获得了自己的模具照片。对于以前从未见过的人,以下是Ryzen处理器的每个核心模样。在基于Zen 2的Ryzen,EPYC和即将推出的Ryzen Threadripper处理器中使用相同的模具: