作为JST PRESTO计划的一部分,东京大学工业科学研究所副教授小林正治(Masaharu Kobayashi)开发了一种具有铁电HfO2和超薄IGZO通道的铁电FET(FeFET)。已经证明了比多晶硅通道更高的亚阈值摆幅(SS)和迁移率。

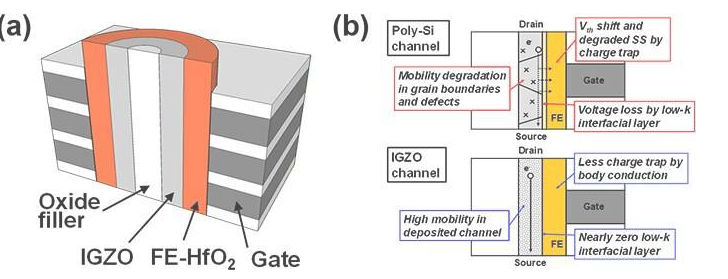

FeFET因其低功耗,高速和大容量而成为有前途的存储设备。在发现了与CMOS兼容的铁电HfO2材料后,FeFET引起了更多关注。为了获得更高的存储容量,已经提出了如图1(a)所示的3-D垂直堆栈结构。

对于3-D垂直堆叠结构,通常将多晶硅用作沟道材料。然而,由于晶界和外在缺陷,多晶硅在纳米厚度区域中具有非常低的迁移率。此外,多晶硅与铁电HfO2栅极绝缘体形成低k界面层。如图1(b)所示,这分别导致电压损失和电荷捕获,这阻止了低压操作并降低了可靠性。

为了解决这些问题,在这项研究中,我们提出了具有超薄IGZO沟道的基于铁电HfO2的FeFET。IGZO是一种金属氧化物半导体,可避免与铁电HfO2栅极绝缘体形成低k界面层。此外,由于IGZO是N型半导体,通常用于无结晶体管操作,因此如图1(b)所示,可以避免电荷捕获,这在反相模式操作中是一个严重的问题。

首先,我们系统地研究了最佳的IGZO通道厚度。随着IGZO厚度的减小,SS减小,阈值电压(Vth)增大。为了实现陡峭的SS和常关工作,选择了8nm。接下来,我们制造了TiN / HfZrO2/ IGZO电容器。HfZrO2是铁电层。截面TEM图像显示如图2(a)所示均匀地形成各层。取得GIXRD光谱并确认铁电相。通过电学表征,如图2(b)所示,我们用IGZO封盖了HfZrO2确认了明确的铁电性能。

应该注意的是,在当前的器件设计中,需要带有掩埋氧化物的背栅来固定体电位。如果没有背栅,则体电位会浮动,并且无法在铁电HfO2栅绝缘体上充分施加电压,这已通过TCAD仿真得到了证实。基于这些器件设计,我们制造了具有铁电HfO2和超薄IGZO沟道的FeFET。图3(a)显示了施加写和擦除脉冲电压后测得的漏极电流与栅极电压的关系。获得了一个0.5V的存储窗口和接近60mV / dec的理想SS。另外,如图3(b)所示,场效应迁移率约为10cm2 / Vs,可以高于相同厚度的多晶硅。

这项研究的成果将为实现具有3D垂直堆叠结构的低压和高度可靠的FeFET开辟新的道路。这导致启用超低功耗的IoT边缘设备,部署高度复杂的网络系统,从而利用大数据提供更具战略意义的社交服务。